更多“D触发器的CP和D的波形如图4.2.59所示,分别画出正边沿…”相关的问题

更多“D触发器的CP和D的波形如图4.2.59所示,分别画出正边沿…”相关的问题

第3题

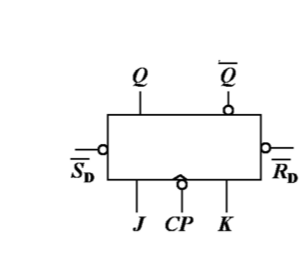

图题4.10是利用上升沿JK触发器CD4027构成,已知CP、R、J、K的电压波形如图所示,试画出输出端Q和端的电压波形。

图题4.10是利用上升沿JK触发器CD4027构成,已知CP、R、J、K的电压波形如图所示,试画出输出端Q和

第5题

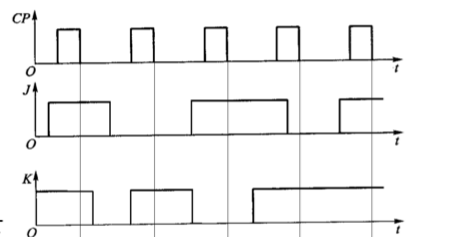

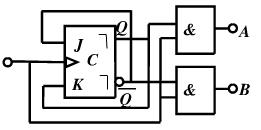

由JK触发器组成的电路如图所示,试写出电路的状态方程,并画出在 CP作用下Q1、Q2、、2的波形(至少4个CP周期,各

由JK触发器组成的电路如图所示,试写出电路的状态方程,并画出在

CP作用下Q1、Q2、

第6题

图13.11(a)所示是用JK触发器组成的双相时钟电路。若CP端加上时钟脉冲信号,在输出端可得到相位互相错开的时钟

图13.11(a)所示是用JK触发器组成的双相时钟电路。若CP端加上时钟脉冲信号,在输出端可得到相位互相错开的时钟信号A和B,试画出Q, 和A,B的波形,假设触发器的初始状态为0。

和A,B的波形,假设触发器的初始状态为0。

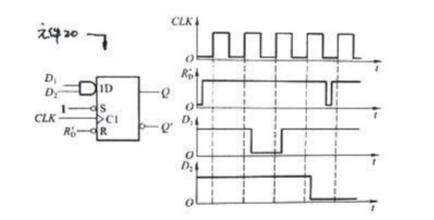

第8题

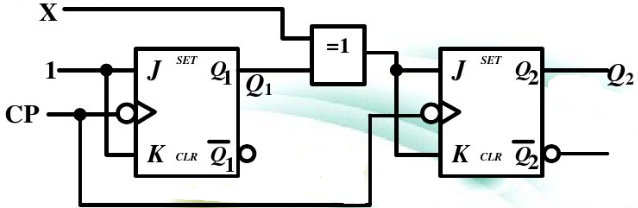

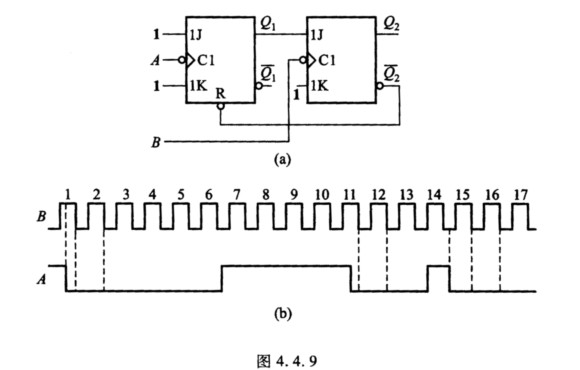

在图4.4.9(a)所示电路中,已知A、B波形如图4.4.9(b)所示,触发器的初始状态均为0,对应试画出Q1和Q2

在图4.4.9(a)所示电路中,已知A、B波形如图4.4.9(b)所示,触发器的初始状态均为0,对应试画出Q1和Q2波形。

第9题

图题6.6的整形电路中,输入电压v1的波形如图中所示。假定它的低电平持续时间比R、C电路的时间常数大得多。 (1)

图题6.6的整形电路中,输入电压v1的波形如图中所示。假定它的低电平持续时间比R、C电路的时间常数大得多。

(1)试画出输出电压的波形。

(2)能否用图题6.6中的电路作单稳态触发器使用?说明理由。

第10题

用集成施密特电路和集成单稳态触发器74121构成的电路如图9.6.3所示。已知施密特电路的VDD=10 V,R=

100 kΩ,C=0.01μF,VT+=6.3 V,VT-=2.7 V;Cext=0.01μF,Rext=30 kΩ。 (1)分别计算vC的周期和vO2的脉宽。 (2)根据计算结果,画出vC,vO1,vO2的波形。

点击查看答案

.jpg)

如果结果不匹配,请

如果结果不匹配,请